Rust로 작성해 보는 컴퓨터 구조 (3) - AND 게이트

AND 게이트는 트랜지스터를 조합해서 만든다. 이름이 AND 게이트인 이유는 트랜지스터를 조합한 회로가 불리언 AND 연산과 동일한 동작을 하기 때문이다.

{ height=45% }

{ height=45% }

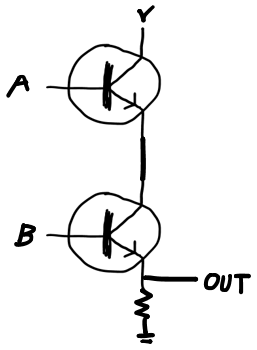

위 그림은 AND 게이트를 트랜지스터 두 개로 만든 것이다. A와 B가 입력이다. A, B 입력에 따라 OUT 출력이 바뀐다. 입력에 따라 바뀌는 출력은 다음 표와 같다.

| 입력 A | 입력 B | 출력 |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

입력에 따른 출력 결과가 불리언 AND 연산과 정확히 일치한다. 전기 회로로 수학적 불리언 연산을 할 수 있다는 뜻이다. 실세계에서 AND 게이트를 트랜지스터 조합으로 만들 수 있으므로 앞장에서 만든 트랜지스터 모델을 조합해서 AND 게이트를 모델링 할 수 있다.

{caption="and_gate.rs | AND 게이트 모델"}

use crate::transistor;

pub struct Andgate {

pub conn_a: bool,

pub conn_b: bool,

pub conn_out: bool,

tr1: transistor::Transistor,

tr2: transistor::Transistor,

}

impl Andgate {

pub fn new() -> Andgate {

Andgate {

conn_a:false,

conn_b:false,

conn_out:false,

tr1:transistor::Transistor::new(),

tr2:transistor::Transistor::new(),

}

}

}

impl Andgate {

pub fn proc(&mut self, input_a: bool, input_b: bool) -> bool {

self.conn_a = input_a;

self.conn_b = input_b;

self.tr1.conn_c = true;

self.tr2.conn_c = self.tr1.proc(input_a);

self.conn_out = self.tr2.proc(input_b);

return self.conn_out;

}

}AND 게이트 회로를 그대로 코드로 모델링한 것이다. 3번째 줄에서 10번째 줄까지가 AND 게이트 모델의 구성 요소를 선언한 코드다. 신호선이 3개고 트랜지스터가 두 개다. 신호선은 외부에서 연결 가능하므로 public으로 선언했고 트랜지스터 두 개는 내부 요소이므로 private이다. 러스트에서는 아무 지시자를 붙이지 않으면 구조체 멤버 변수는 private다.

12번째 줄에서 22번째 줄은 AND 게이트 객체를 생성하는 생성자 함수다. 신호선 세 개는 기본값이 false이고 트랜지스터 두 개에 객체를 생성했다.

24번째 줄에서 34번째 줄이 AND 게이트 동작이다. 30번째 줄에 tr2의 conn_c의 입력으로 tr1.proc() 메소드 결과를 넣었다. 이 코드가 AND 게이트 회로 그림에서 첫 번째 트랜지스터의 E와 두 번째 트랜지스터의 C가 연결된 그림을 모델링한 코드다.

AND 게이트 회로의 결과는 두 번째 트랜지스터의 E 신호선 값이다. 그래서 31번째 줄과 33번째 줄을 보면 tr2.proc() 메소드의 결과를 conn_out에 넣어서 리턴한다.

제대로 모델이 동작하는지 테스트한다. 테스트 방법은 앞장의 인버터와 트랜지스터 테스트 방법과 같다. main() 함수에서 모델의 동작 결과를 출력해서 눈으로 확인해 보는 것이다.

{caption="main.rs | AND 게이트 모델 테스트"}

mod and_gate;

fn main() {

// ...생략...

let mut and_gate = and_gate::Andgate::new();

println!("Test AND Gate, (0, 0) -> {}", and_gate.proc(false, false));

println!("Test AND Gate, (0, 1) -> {}", and_gate.proc(false, true));

println!("Test AND Gate, (1, 0) -> {}", and_gate.proc(true, false));

println!("Test AND Gate, (1, 1) -> {}", and_gate.proc(true, true));

}불리언 AND 연산의 진리표에 맞게 동작하는지 확인하는 코드다. 그래서 입력 A, B에 true, false 입력 조합을 모두 넣었다. 출력 결과가 불리언 AND 연산의 진리표와 일치하면 모델이 제대로 동작하는 것이다.

$ cargo run

... 생략 ...

Test AND Gate, (0, 0) -> false

Test AND Gate, (0, 1) -> false

Test AND Gate, (1, 0) -> false

Test AND Gate, (1, 1) -> true

테스트를 실행한 결과를 보면 불리언 AND 연산의 진리표와 일치한다. AND 게이트 모델이 제대로 동작함을 확인했다.

{ width=50% }

{ width=50% }

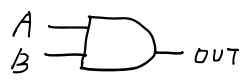

AND 게이트를 회로도에 그릴 때는 위 기호를 사용한다.

| 첨부 | 파일 크기 |

|---|---|

| 16.33 KB | |

| 4.1 KB |

댓글

앞에서 만들었던 트랜지스터 객체를 사용해서 AND

앞에서 만들었던 트랜지스터 객체를 사용해서 AND 게이트를 만들었습니다.

다음편은 OR 게이트입니다.

----------------------

얇은 사 하이얀 고깔은 고이 접어서 나빌레라

댓글 달기