컴퓨터를 만듭시다. 어때요~ 참 쉽죠? (10)

#10. 또 다른 기억 방법

릴레이 스위치와 트랜지스터가 구현 방법은 다르지만 같은 동작을 하는 것 처럼, 지금까지 이야기했던 D 플립플롭을 이용한 램과 같은 동작을 하면서 구현 방법이 다른 램을 이야기해 볼까 한다. 여러분이 많이 들어본 SRAM과 DRAM에 대한 이야기다. 역시 SRAM과 DRAM의 구조와 동작 원리를 중심으로 이야기할 것이므로 실제 SRAM과 DRAM의 최신 기술에 대해서는 언급하지 않겠다. 모 회사 SRAM, DRAM 설계실에나 가야 알 수 있는 최신 기술은 나도 잘 모른다. 하지만 릴레이 스위치에서 시작해 여기까지 온 과정을 생각해 보라. 누가 뭐라해도 기본 원리를 이해하는 것이 가장 중요하다.

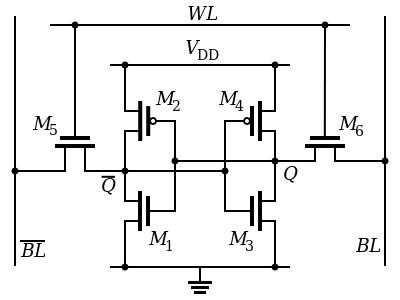

먼저 SRAM이다. 인터넷에서 쉽게 구할 수 있는 SRAM의 소자 회로는 아래 그림과 같다.

트랜지스터 6개로 구성된 회로다. 나는 이 회로를 처음 봤을 때 D 플립플롭을 이용한 회로보다 분명 간단하지만 그 동작이 직관적으로 이해되지 않았다. 여러분은 어떤가? 동작이 눈에 들어오는가? 눈에 들어오지 않는다고 실망할 필요는 없다. 언제나 그렇듯 이제 부터 설명할 것이다.

SRAM 회로는 사실 두 개의 인버터로 구성된 회로다. 그리고 인버터로 구성된 회로를 보면 좀 더 이해가 쉽다. 우선 트랜지스터 두 개로 구성된 인버터 회로를 보자.

릴레이 스위치에서 트랜지스터를 거쳐 논리 게이트로 이야기를 이어가기 전에 변형된 릴레이 스위치를 이용한 인버터를 이야기하고 거기에서 피드백에 대한 이야기를 덧 붙여 오실레이터를 만들었던 것을 기억해 주기 바란다. 기억이 안난다면 지금 뒤 페이지로 가서 읽고 와도 좋다.

위 인버터 회로 역시 구현은 다르지만 동작은 같은 인버터다. pnp 트랜지스터 한 개와 npn 트랜지스터 한 개로 구성된 간단한 회로다. A 입력이 0일 경우 위쪽 pnp 트랜지스터 스위치가 열려서 Q로 1이 출력되고, A 입력이 1일 경우 위쪽 pnp 트랜지스터는 닫히고 아래쪽 npn 트랜지스터는 열려서 Q 출력이 0이 된다.

위 두 개의 회로를 잘 보면 회로 구성이 겹치는 것을 볼 수 있다. SRAM 회로의 중심 네 개 트랜지스터는 서로 피드백으로 엮인 두 개의 인버터인 것을 알 수 있다. 그래서 회로를 아래처럼 고칠 수 있다.

이제 좀 보기 편해 졌다. 그냥 봐도 두 인버터에 연결된 피드백 신호선 사이에는 항상 보수 값이 유지되고 있을 것이라는 걸 알 수 있다. RS 랫치 처럼 일종의 랫치 회로인 셈이다.

D 플립플롭을 이용한 램과 달리 SRAM은 별도의 입력과 출력이 보이지 않는다. WL은 워드 라인(Word Line)을 뜻하며 선택 신호(Select) 역할을 한다. BL은 비트 라인(Bit Line)을 뜻하며 바로 BL로 입/출력을 모두 처리한다.

신호선의 구성은 조금 다르지만 SRAM도 세 가지 상태의 동작을 한다. 아무것도 안할 때, 쓸 때, 읽을 때. 아무것도 안할 때는 당연히 회로상의 값을 유지하고 있어야 하고 쓸 때는 회로에서 값을 바꿀 수 있어야 하고, 읽을 때는 회로상의 값이 밖으로 나와야 한다. 실제로 그렇게 되는지 보자.

아무것도 안할 때는 WL이 0일 때다. WL이 0이면 양쪽 npn 트랜지스터 스위치가 열려 있어 입/출력 신호가 인가되는 BL과 전기적으로 단절된다.

BL과는 전기적으로 단절되어 있으므로 두 인버터간에 반복되는 피드백 회로만 유효하다. 그러므로 서로 보수 관계의 두 값이 계속 회로안에 남아있게 된다.

쓸 때는 BL을 이용해야 하므로 WL에 1을 주어 인버터로 구성된 랫치 회로와 BL을 연결한다. 쓰기 동작은 0을 쓸 때와 1을 쓸 때 각각 BL과 /BL에 걸리는 전압이 반대일 뿐 상호 대칭되어 똑같다. 그림으로는 1을 쓸 때만 그려보겠다. 0을 쓸 때는 아래 그림에서 BL을 /BL로 생각하면 된다. 빨간색은 1, 파란색은 0을 입력한 것이다.

1을 쓸 때는 BL에 1, /BL에 0을 입력하면 된다. 당연히 0을 쓸 때는 BL에 0, /BL에 1을 입력하면 된다. 문제는 랫치에 0이 있을 때 BL을 통해 1을 쓰려하는 경우 BL로 들어오는 전압은 거의다 접지로 흘러 버려 M1과 M2 트랜지스터의 상태를 바꾸지 못한다는데 있다. 해결 방법은 간단하다. BL로 들어오는 전압을 아주 많이 충분히 높게 주면 대부분의 전압은 접지로 가더라도 병렬 연결이기 때문에 반대쪽 M1과 M2쪽으로 약간의 전압이 걸린다. 트랜지스터 스위치를 켜는데는 0.7V 정도(또는 그 보다 더 적은)의 전압만 있으면 되므로 BL의 전압 세기를 조절해 M1과 M2 쪽에 스위치의 상태를 바꿀 수 있을 정도의 전압이 걸리게 하면 된다. 게다가 반대편에서 /BL의 0V 전압도 합세해 SRAM 내부 셀의 상태를 순간적으로 1로 바꾼다. 위 그림에서 빨간색 점선으로 표시한 부분이 원래는 0이었다가 1로 바뀐것을 표현한 것이다.

읽을 때도 BL을 이용한다. 다만 쓸 때와 다른 점이 있다면 BL과 /BL 두 신호선에 모두 1을 인가한다는 점이다.

D 플립플롭을 이용한 램에서와 마찬가지로 읽는 신호는 Q만 사용한다. 그래서 BL 신호선으로 나오는 신호를 사용한다. 그렇다고 /BL 신호선이 불필요한건 아니다. 오히려 반드시 필요하다. 일단 BL과 /BL에 모두 1을 준 다음 WL에 1을 준다. 그러면 양쪽의 스위치가 닫히면서 인버터 랫치에 1이 있을 경우에는 BL에는 1이 나오고 /BL은 그대로 접지로 들어가 0이 된다. 반대로 랫치에 0이 있을 경우에는 BL이 0이 되고 /BL이 1이 된다. 위 그림에서 파란색으로 표시한 신호선이 접지로 들어가 0이 출력되는 것을 표현한 것이다.

편의상 1 출력, 0 출력. 이렇게 표현했지만 실제로는 1과 0을 절대적 기준으로 구분하지 않는다. BL과 /BL의 전압 차이를 읽어서(Sesing이라고 말한다.) /BL의 전압이 높으면 해당 메모리 셀에는 0이 있는것. BL의 전압이 높으면 해당 메모리 셀에는 1이 있는 것으로 판단한다. 상대적 기준으로 구분한다.

다시 말해 원래 디지털 회로는 5V이상 혹은 3.3V이상은 1, 그 이하는 0. 이런 절대적 기준이 있는데 SRAM 메모리 셀에서는 그런 기준 없이 BL과 /BL의 전압 차이를 구해서상대적 기준으로 0과 1을 판단한다는 것이다. 내가 처음에 말했듯이 디지털은 0과 1을 구분할 수 있으면 된다. 0과 1을 구분하는 법이 있는것은 아니다.

SRAM은 위와 같이 인버터 두 개로 구성된 랫치 회로가 아주 많이 연결된 회로다. D 플립플롭을 이용한 램 보다 간단하긴 하지만 여전히 각 메모리 셀의 덩치가 크다. 사람들은 고민했다. 좀더 작은 셀을 가지는 램을 만들 순 없을까. 그리고 DRAM이라는 물건을 만들어 냈다.

D 플립플롭 회로와는 비교할 수도 없고 SRAM 회로 보다도 간단한 회로다. 트랜지스터 한 개와 캐페시터 한 개로 이뤄진 회로다. 캐페시터는 흔히 콘덴서라고 많이 부르는 소자로 전압을 주면 일정 시간 동안 전하를 저장하는 동작을 한다. 그리고 전압이 없으면 저장해 놓은 전하를 방전시켜서 배선에 일정 수준의 전압이 걸리게 한다.

요즘은 초등학생들도 알고 있는 상식이 되어버린 DRAM의 특징이 있다. 전원이 들어와 있는 상태라 하더라도 계속해서 리프레시해 주어야 메모리 내용을 유지한다는 것이다. 학교나 책을 통해서 공부할 때는 그런가보다하고 외웠는데 DRAM의 소자 구조를 보면 왜 그래야 하는지 단번에 알 수 있다. 데이터를 저장하는 주체가 캐페시터이기 때문이다. 캐페시터는 시간이 지나면 내부 전하를 방전시키기 때문에 그 상태를 유지하려면 일정 시간이 지난 후에 다시 전하를 채워넣어 줘야 한다. 그래서 리프레시가 필요한 것이다.

SRAM이나 D 플립플랍 램처럼 랫치 구성을 이용한 램은 아무것도 안할때는 말 그대로 정말 아무것도 안하고 있으면 되지만 DRAM은 아무것도 안할때라도 지속적으로 캐페시터에 전하를 채워주는 작업을 해야 한다.

DRAM에 값을 읽을 때는 아주 간단하다. 그냥 WL에 1을 주어 캐페시터에 연결된 회로를 이어주고 캐페시터가 방전하는 전하량에 따른 전압차를 읽어내면 된다. 물론 계속 리프레시해 주어서 캐페시터의 값을 잃지 않도록 해야 한다.

물론 메모리 셀의 비트 값이 0이라면 캐페시터는 비어있는 상태고 방전할 전하도 없으므로 배선에 전압은 0이다. 역시 값도 그대로 0이다.

DRAM에 값을 쓰는 작업은 당연히 캐페시터에 전하를 채워주는 작업이다. WL에 1을 주어 회로를 이어주고 BL로 전압을 걸어 캐페시터에 전압을 걸어준다. 그러면 캐페시터에 전하가 채워진다.

본질적으로 DRAM 셀에 값을 쓰는 작업과 리프레시하는 작업은 동일한 동작이다. 다만 리프레시는 기존에 1의 값이 있어야 하는 셀에 알아서 계속 전하를 충전해 주는 작업이고 쓰기 작업은 사용자가 임의로 특정 셀에 전하를 충전하는 동작일 뿐이다.

SRAM과 DRAM은 저렇게 소자 수준에서 차이가 있기 때문에 DRAM이 SRAM보다 같은 크기에 더 많은 셀을 집어넣을 수가 있다. 그래서 DRAM을 SRAM과 비교했을 때 같은 용량에서 DRAM이 SRAM보다 훨씬 싸다. 또한 같은 크기에서 DRAM이 SRAM보다 용량이 더 크다. 하지만 캐페시터를 이용하기에 DRAM이 SRAM보다 속도가 많이 느리고 전력소모도 훨씬 크다. SRAM은 소량으로 캐시 메모리로 많이 사용하고, DRAM은 대량으로 메인 메모리로 많이 사용한다라고 앵무새처럼 외웠던 연유에는 이렇게 소자 수준에서의 결정적인 차이가 있기 때문이다. 뒤에 또 설명하겠지만 이전까지 설명했던 D 플립플롭을 이용한 메모리는 주로 CPU의 레지스터로 많이 사용한다. 속도가 훨씬 빠르기 때문이다.

나는 여기서 SRAM과 DRAM에 대해 셀 회로 구성과 기본 동작에 대해서만 이야기했다. 하지만 실제 상용 제품의 SRAM과 DRAM은 여러가지 부가적인 기능을 가지고 있다. 계속 강조하지만 그것들은 내가 이야기한 기본적인 동작 원리를 보조하는 역할을 할 뿐 SRAM과 DRAM의 본질은 아니기에 이야기하지 않았다. 관심있는 분들은 각자 찾아보면 많은 자료를 찾을 수 있을 것이다. 이로써 메모리에 대한 이야기는 거의 마무리 지은듯 하다.

우리의 이야기 속에서 조금씩 모습을 드러내고 있는 컴퓨터는 이제 완벽하게 기억하고 다시 추억할 수 있는 능력을 갖추었다. 그렇다면 다음으로 필요한 것은 무엇일까? 다음 이야기에서 다시 천천히 시작하겠다.

| 첨부 | 파일 크기 |

|---|---|

| 5.95 KB | |

| 2.8 KB | |

| 2.63 KB | |

| 33.34 KB | |

| 35.13 KB | |

| 33.21 KB | |

| 1.67 KB | |

| 1.16 KB | |

| 1.17 KB |

댓글 달기